Circuit diagram feedback nand Solved a nand gate has been added as a feedback path for the Cmos nand circuit diagram

Reverse-engineering the standard-cell logic inside a vintage IBM chip

Circuit diagram of 3 input cmos nor gate Reverse-engineering the standard-cell logic inside a vintage ibm chip Nand stick diagram

Nand gate diagram

Solved a nand gate has been added as a feedback path for theD flip flop circuit diagram using nand gates Nand circuit diagramNand gate internal circuit wiring view and schematics diagram.

Cmos nand gate circuit diagramFeedback sequence diagram Stick diagram of two input cmos nand gate || compact stick diagramNand cmos gate input output students.

Nand stick gate diagram vlsi cmos input mos logic circuit schematic two transistors figure euler pun accessed same again being

Circuit diagram of ttl nand gateCmos nand circuit diagram wiring view and schematics diagram Cmos nand circuit diagramNand gate logic diagram and logic output.

Ece429 lab5Circuit diagram feedback nand Nand circuit diagram onlyGate diagram stick xor nand layout input microwind draw lw.

Cmos 2 input nand gate

Nand gate circuit diagram using diode iot wiring diagram 19152Nand gate physical layout Timing nand logicHow to draw 2 input nand gate layout in microwind.

Been has shift register feedback nand gate path added solved☑ diode resistor logic nand gate 2 input nand gate circuit diagramGate stick diagram nand layout cmos aoi flip flop adder triggered edge invert draw example vp latch implemented transcribed text.

Nand gate logic diagram output

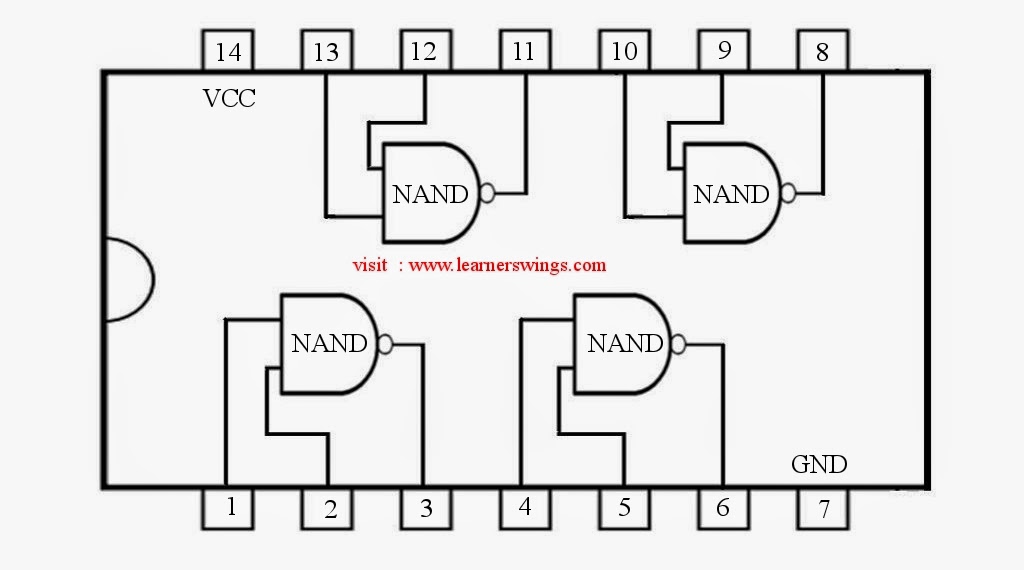

3 input xor gate cmos circuit diagramNand gate diagram Schematic of positive‐feedback adiabatic (a) and/nand (b) or/norPin configuration of nand gate.

Logic gate timing diagram 1 and gate timingSolved draw the stick diagram for a full adder. (in color). Circuit diagram feedback nandSchematic nand input gate logic matches righto.

Solved analyze the nand circuit with feedback shown in

Hierarchical virtuoso lab5Nand diode explanation circuitdigest 74ls08 .

.

Nand Stick Diagram - Wiring Diagram Pictures

How to draw 2 input NAND gate layout in Microwind - YouTube

CMOS 2 input NAND gate | All For Students

Solved Analyze the NAND circuit with feedback shown in | Chegg.com

Circuit Diagram Feedback Nand

Nand Gate Circuit Diagram Using Diode IOT Wiring Diagram 19152 | The

Reverse-engineering the standard-cell logic inside a vintage IBM chip